Intel reveals transistor scaling breakthroughs at 2023 IDEM

Mon, 11th Dec 2023

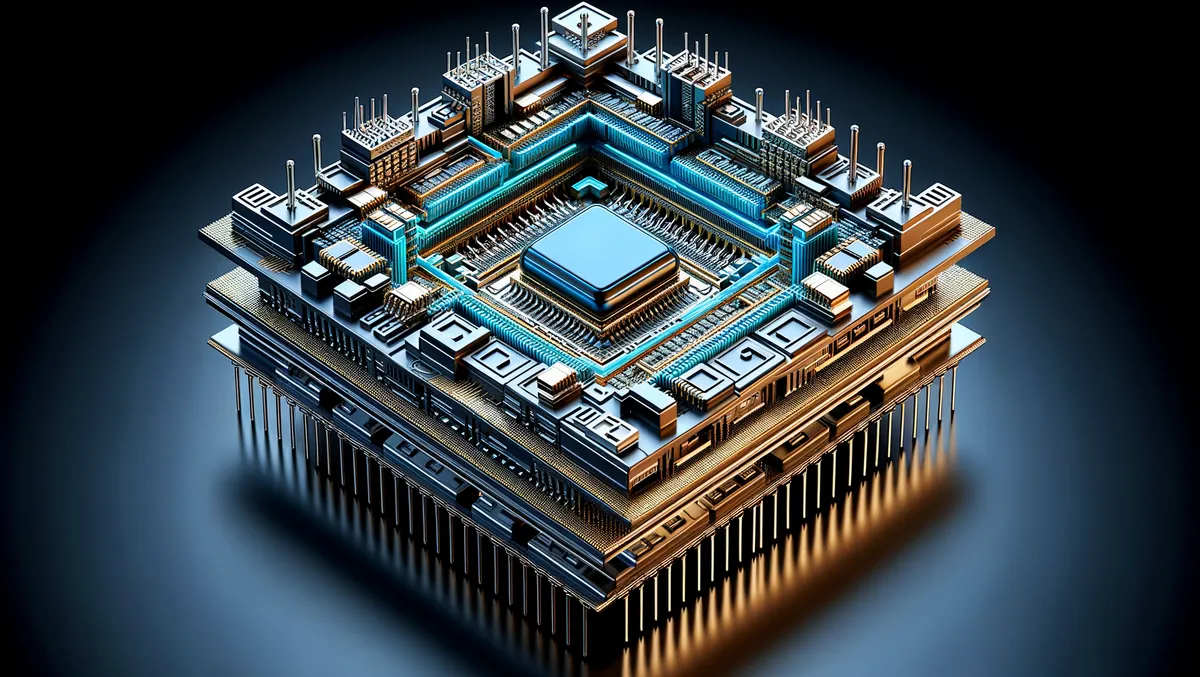

At the IEEE International Electron Devices Meeting 2023 (IDEM), Intel shared significant breakthroughs in next-generation transistor scaling. Demonstrating a comprehensive pipeline of innovative methods for the company's future process roadmap, Intel's advancements indicate the persistent evolution of Moore's Law. The technology giant showcased developments in 3D stacked complementary metal oxide semiconductor (CMOS) transistors, featuring backside power and direct backside contacts. These pioneering initiatives underline the ongoing criticality of transistor scaling and backside power in meeting the exponentially increasing demand for high-performing computing.

Industry professionals are expressing excitement over the first-of-its-kind advancements displayed by Intel, which will aid the extension of Moore's Law. Intel's Components Research team demonstrated the integration of silicon transistors with gallium nitride (GaN) transistors on a single 300-millimetre wafer - a seismic industry first. "As we enter the Angstrom Era and look beyond five nodes in four years, continued innovation is more critical than ever... underscoring our ability to bring leading-edge technologies that enable further scaling and efficient power delivery for the next generation of mobile computing," said Sanjay Natarajan, Intel senior vice president and general manager of Components Research.

Among the impactful achievements presented by Intel was the company's industry-first construction of 3D stacked CMOS transistors, combined with backside power and direct backside contacts. This accomplishment underscores the company's leadership in gate-all-around transistors, showcasing Intel's lead over competition and capacity to innovate beyond RibbonFET. Part and parcel of Intel's research agenda are also the scaling strategies for breakthroughs in backside power delivery, such as backside contacts. These technologies are anticipated to be integrated into production during this decade.

Looking towards the future, Intel has committed to innovating the incorporation of more transistors on silicon for enhanced performance. They have identified key research and development areas necessary for continued scaling through efficient stacking of transistors. The Components Research team has presented projections for Moore's Law to extend up to a trillion transistors on a package by 2030. This innovation orients around enhancements in backside power delivery and the application of innovative 2D channel materials.

Further advancements lie in the integration of silicon transistors with GaN transistors on the same 300-millimetre wafer, offering high-performance, large-scale integrated circuit solutions, known as "DrGaN", optimised for power delivery. Intel has been the first to verify the capability and performance of this technology, which promises to match the power density and efficiency demands of future computing.

Intel has made further strides in advancing research and development within the 2D transistor space, buttressing future scalability in line with Moore's Law. Prototypes of high-mobility transition metal dichalcogenide transistors for both NMOS and PMOS have been demonstrated, in addition to presenting the industry's first gate-all-around 2D PMOS transistor on a 300-millimetre wafer, marking another set of industry-first achievements for Intel.